The core of the electronic enthusiast network : Cadence FPGA System Planner (FSP) is a high integrity FPGA-PCB systematic collaborative design tool. This time mainly introduces the basic situation of FPGA System Planner, see the original text.

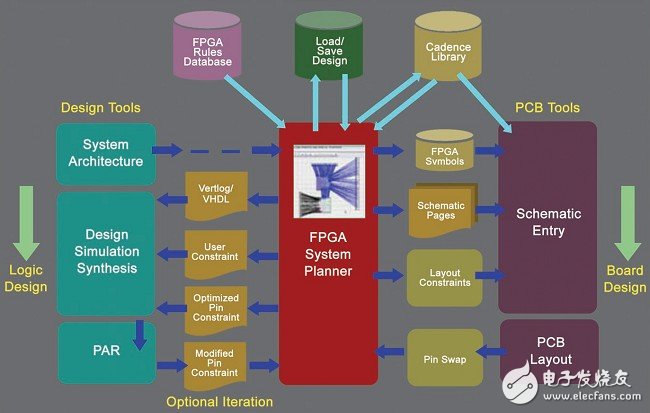

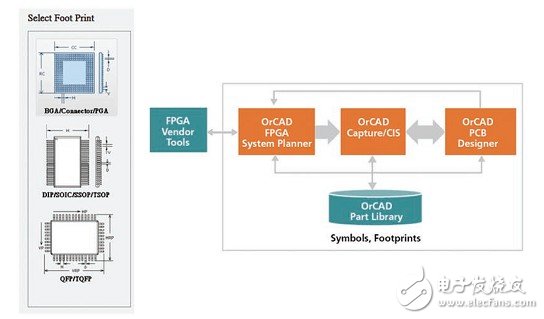

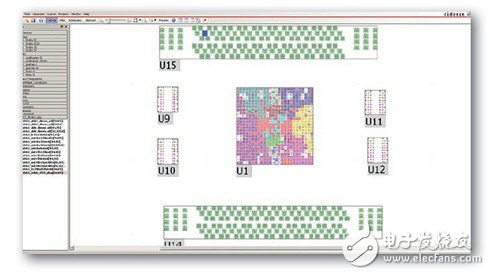

There are almost a thousand programmable I/O pins in newer FPGA designs. If you include multiple FPGAs, engineers will encounter initial planning I/O pins and how to deal with later layout placement. Optimized bottlenecks and difficulties. Cadence OrCAD and Allegro FPGA System Planner can meet more complex designs and produce optimal I/O pin planning at the beginning of the design, and can be systematically designed through FSP, while integrating logic, schemaTIc, PCB synchronization planning Single or multiple FPGA pin optimization and layout placement, with integrated interface to reduce duplication of testing and correction process and communication time in design and PCB layout, even through optimized pin mapping, placement Saves more space or stacking, and FSP not only speeds time-to-market but also saves design costs.

Figure 1 High-integrity FPGA-PCB systematic collaborative design tool

Specifying Design Intent

In the FSP integration tool, the parts to be placed can be directly selected from the parts library, and these parts can directly use the packaging in the PCB, and let us plan the FPGA design and the placement on the PCB in advance.

In terms of design, customers can directly define the connection relationship between FPGA and other parts, save time in other tool designs and then transfer to SchemaTIc, PCB. The currently used DDR2, DDR3, PCI Express designs can be generated by FSP. Connection between FPGA and memory DIMM or multiple FPGAs.

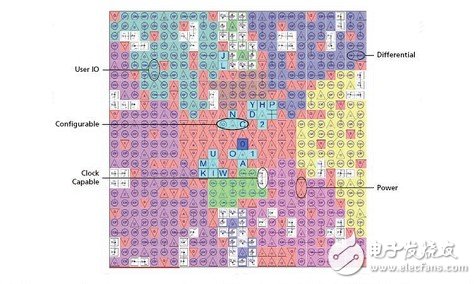

FPGA Device Rules

The FSP library contains FPGA models, which specify the location and electrical characteristics of the pin pins provided by the FPGA vendor.

Germany type 16A 250V~, IP20, Class I, non-rewirable, single-way socket outlet complies ,with shutter, with a non-rewirable plug, with cord H05VV-F 3G1,0-1,5mm 2 (max length be 2m for 1,0mm 2 and 30m for 1,5mm2 ).

16A 250V~, IP20, Class II, non-rewirable, with single way socket-outlet with shutter, with a non-rewirable plug, with flexible cord H05VV-F (with or without fabric braided cover) 2G1,0-1,5mm 2 (Max. 2m for 1,0mm 2 in length and Max.30m for 1,5mm 2 ).

Germany Extension Cord,Power Strip Extension Cord,European Extension,Eu European Power Extension Cord

CIXI KYFEN ELECTRONICS CO.,LTD, , https://www.kyfengroup.com