Does your development team need to create a new generation of systems that are both complex and competitive in a very short time? Xilinx All Programmable devices can help you with software programmable ARM processing systems, programmable analog mixed-signal (AMS) subsystems, and a rich set of high-complexity compared to traditional programmable logic and I/O. IP, supporting the development team to break through the original design constraints. Xilinx has a wide selection of All Programmable devices to choose from, and the various silicon combinations that make up these devices are interconnected using Xilinx's unique high-performance 3D stacked silicon interconnect technology. These leading-edge All Programmable devices provide users with features that go far beyond conventional programmable logic and open up a new era of comprehensive programmable system integration for users.

The significance is that with Xilinx All Programmable devices, users' development teams can implement more system functions with fewer components, improve system performance, reduce system power consumption, reduce bill of materials (BOM) costs, and meet stringent product launches. time requirement. But without the help of powerful hardware, software, system design tools, and design processes, you can't put these benefits into the hands of your design team, and you can't realize these advantages. Xilinx refers to these hardware, software, and system design development processes collectively as "All Programmable AbstracTIon."

The Xilinx Vivado Design Suite plays a central role in this advanced generation of hardware, software and system development using All Programmable abstraction. The Vivado Design Suite is a new generation of new SoC-enhanced integrated development environment centered on IP and systems that addresses the productivity bottlenecks that are common in system-level integration and implementation.

While competing solutions are still trying to keep up with the rapid development of on-chip integration by extending outdated and loosely connected discrete tools, the Vivado Design Suite offers unique, high-level performance with the industry's most advanced SoC-enhanced design methods and algorithms. The integrated development environment brings designers a tremendous increase in design productivity. The Vivado Design Suite takes the productivity of hardware, software and systems engineers to a whole new level.

The following nine reasons will give you an idea of ​​why the Vivado Design Suite delivers leading-edge design productivity, ease of use, and powerful system-level integration.

Speed ​​up system implementation

Reason one: Break through device density limits: Integrate more features faster in a single device

If the design tool enables All Programmable devices to integrate more functions, the user can select the smallest possible device in the system design, which directly leads to a reduction in system cost and power consumption. The Vivado Design Suite provides an integrated environment that enables architecture, software, and hardware developers to work together in a common design environment to maximize design efficiency and leverage the programmable logic architecture of All Programmable devices and their dedicated on-chip functional blocks. potential.

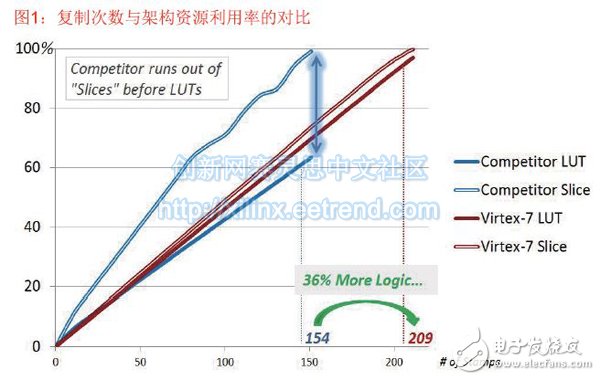

Take OpenCores.org's Ethernet MAC (Media Access Controller) module design as an example. As an experiment, Xilinx replicated the OpenCores Ethernet MACs as they were until they were filled with Virtex-7 690T FPGAs with 693,120 logic cells. Xilinx has similarly filled competing devices with 622,000 logic cells. The figure below shows the experimental results.

Measured by the number of logical units (a "standard" logic unit consists of a 4-input LUT (lookup table) and a flip-flop), the Xilinx Virtex-7 690T device has a raw capacity that is comparable to competing devices (with 622, 000 logical units) 11% higher. But as shown in Figure 1, if all of these Ethernet MAC module instances are populated into the Xilinx Virtex-7 690T device with the Vivado Design Suite, the Xilinx Virtex-7 690T device has more instances than competing devices. 36%. This experiment shows that the efficiency of the Vivado Design Suite in combination with the Xilinx 7 Series FPGA architecture is much higher than the efficiency of competing tools/device combinations.

(Note: Figure 1 compares Xilinx 7 Series All Programmable devices with competing programmable logic devices based on LUT and Slice count results. Xilinx 7 Series All Programmable device slices contain four 6-input LUTs, eight triggers And the associated multiplexer and arithmetic carry logic, which is equivalent to 1.6 logic cells.)

How the Vivado Design Suite maximizes device utilizationThe Vivado Design Suite enables higher device utilization because it uses advanced fitting algorithms and the Xilinx 7 Series programmable logic architecture uses a truly independent LUT in each slice. It is worth noting that Figure 1 details the LUT and Slice fitting results of the Xilinx 7 Series, both achieving nearly 100% utilization. Competing programmable logic devices use up the available slices when the device utilization is only 63%. The root cause of this low utilization is due to the programmable logic architecture of the competing device, which in many cases does not allow the two LUTs to be bundled into one physical cluster. In a complete design, this obviously creates a large number of underutilized clusters. This is because in order to meet the pin sharing requirements of the architecture, only one LUT is used, and the other LUT can no longer be used for the rest of the logic in the design. This experiment clearly shows that users can use the smaller 7 Series All Programmable to achieve greater system design.

12Inch Coaxial Speaker,12 Inch Coaxial,12 Inch Neodymium Coaxial Speaker,12 Inch Coaxial Speaker

Guangzhou BMY Electronic Limited company , https://www.bmy-speakers.com